#### Activity Counter:

## a New Optimization for SIMD Control Flow (extended version)

Ronan Keryell\*

Centre de Recherche en Informatique

École des Mines de Paris

77305 FONTAINEBLEAU Cedex

FRANCE

Nicolas Paris\*

Hyperparallel Technologies

École Polytechnique X-POLE

91128 PALAISEAU Cedex

FRANCE

11 January 1993

#### Abstract

of activity bits when subsets of subsets are supported. We present an implementation of activity stacks based on counters. At a given stack depth n, the number MIMD computers. is useful for SIMD machines and for compilers of collection-oriented languages on bits. The local controller is of equivalent complexity in both cases. This algorithm of memory bits required is  $\log_2 n$ , whereas previous implementations require n Subsets of processors or data items are implemented via an activity bit and a stack form the same computation on each data item or on just a subset of the data. SIMD computers and collection-oriented languages, like  $\mathbb{C}^*$ , are designed to per-

#### 1 Introduction

sors, to gain use of parallelism on SIMD or MIMD machines. single program is applied on different instances of data, spread across different procesprogram many parallel applications on massively parallel machines. In this model, a The data-parallel programming model is seen as an acceptable solution to efficiently

same operation on each object of the set: Data-parallel collection-oriented languages like MPL [Mas91], C\* [Thi90] or POMPC [Par92] and SIMD<sup>1</sup> computers like the MP-1 [Bla90], the CM-2 [Bla90] or POMP [HKMP91] have in common that they all deal with a set of objects and apply the

• in an SIMD computer there is a unique instruction flow and thus each processor performs the same operation on different data;

<sup>\*</sup>Major parts of this work were made when the authors were with the Laboratoire d'Informatique de l'École Normale Supérieure, 45 Rue d'ULM, 75005 PARIS, FRANCE. This research and the POMP project were partially funded by the French Research and Technology Ministry, Thomson Digital Image, the CNRS (National Center of Scientific Research), the LIENS, the École Normale Supérieure,

the PRC-ANM.

<sup>1</sup>Single Instruction stream, Multiple Data streams.

in a collection-oriented language, the data parallel semantics allow parallel operations on a set of data in a locked-step SIMD way: operations are applied on each

with data parallel control flow. regular data parallel problems. However, it is at least as important to deal correctly goal of these parallel approaches is to obtain maximal performance on straight

the sequential if ...then...else construct. need such a control flow on parallel data. This is the extension in the space domain of mathematical functions, such as the absolute value and many general algorithms also different from the ones used on the interior points. The computation of many classical equation problems, often need to apply different at the boundary conditions which are As a matter of fact, a lot of numerical problems, like solving partial differential

in the synchronous SIMD model, to deal with parallel control flow. model and the need for a local instruction stream, *i.e.* a bounded dissynchronization There seems to be an intrinsic contradiction in the commonly used SIMD control flow

POMP project and our POMPC compiler. Section 7 presents related work. Section 6 presents a general view of the implementation of the method used in our according to time and space complexity, for SIMD and MIMD, hardware and software parallel control flow operators. Section 5 compares the activity stack with our method and section 4 presents our new algorithm with some examples applied to POMPC of data parallel control flow. Section 3 discusses background to generally related work Section 2 presents an abstract of the POMPC language in order to display examples

# N POMPC: a collection-oriented data parallel language

to exhibit the problems related to parallel control flow in some languages with SIMD Although it is not the object of this article, we briefly present a data parallel language

some advantages of C\* [Thi90], MPL [Mas91] and MULTIC [Wav91]. It is: PompC is a superset of the C language similar to the new version of  $C^*$  and gathers

- a data parallel language since it can express computations on parallel data, with element by element interactions, such as additions of vectors or matrices;

- a collection-oriented language since each variable belongs to an equivalence class, a better suited term we introduce for the previous "mask" or "context" (detailed a collection in our language, which defines its size, its geometry and its activity,

such as FORTRAN 90. fact, PompC adopts a microscopic point of view of parallelism, in contrast to languages collection name is a new parallel type that can be combined with the usual C type. In Thus, PompC has a new keyword collection to declare a new collection. The

variable belonging to this collection. a number of dimensions unknown a compile time and v is a parallel double precision and a and b two double precision variables. a\_vector is a collection with a size and In Figure 1, we define a rectangular collection an\_array with  $100 \times 200$  elements

```

void div_by_0()

double a_vector v; /* The parallel size of v is unknown at compile time. */

double an_array a,b; /* a and b are parallel variables of the collection

collection a_vector; /* The size is defined dynamically elsewhere in the program.

collection an_array[100,200];

where (a != 0)

double s = 0;

int i = 0;

elsewhere

elsewhere b = -1/a;

where (a > 0)

;

0

1

9

where (v > 0)

s +<- v;

i++;

b += s;

```

Figure 1: Example in POMPC with where/elsewheres

other interactions are explicit and called communications, but this is not our interest Belonging to the same collection allows variables to interact element by element. All

same collection as specified by the collection of the condition in the operator. or C\*, they can be nested. Each operator has an action only on the variables in the the classical where/elsewhere to select some variable elements. As in ACTUS [Per79] As in most parallel languages, PompC contains parallel control flow operators, like

sponding element in a is 0, the absolute inverse of a when the element of a is negative and the inverse of a plus the sum of all the positive elements of  ${\bf v}$  when a is positive. The function div\_by\_0 of Figure 1 assigns 0 to an element of b when the corre-

not involve the a\_vector collection. the where (v > 0). This where is not affected by the previous wheres since they do duction s + - v is always executed with the selected elements, the active elements, by belong to the an\_array collection controlled by any previous wheres. The scalar re-The scalar operation i++ is always executed since it is scalar code and does not

many virtual SIMD machines in the computer as there are collections in the program. We can consider this microscopic point of view of parallelism as if there were as

neither always possible nor easy to have interprocedural analysis. Also such side effects C language, when source code is not available. may be hidden in libraries because of the mechanism of separated compilation in the functions may have conditional parallel blocks depending on other collections. So it is that it is possible to have calls to functions in a conditional parallel block and these of virtual processors, its own geometry: it is the virtualization. An important point is Each virtual machine is naturally independent and has its own activity, its own number

Therefore, activity resolution is needed at run time.

## ೮ Classical approaches to parallel control flow

instructions for a physical or virtual SIMD machine. tial frame, running on a physical or virtual sequential machine, containing parallel use the same model as Flynn [Fly66] and view an SIMD program as a sequen-

to be a space-time duality: gives it the expected instruction. In comparison with a sequential computer, it appears processing element (PE) cannot influence this stream, it has to wait until the stream an address which will be reached by the global instruction stream. Indeed, since a Conceptually, the parallel control flow can be seen as a jump into the future to

- an "SIMD branch" is a time delay since a PE must wait for the moving of the global instruction stream until the expected instruction is reached;

- a sequential branch (or on the PE of an  $\mbox{\scriptsize MIMD}^2$  computer) is into the space since it can change the value of its program counter and instantaneously jump to another point of the program.

[HLJ+91]. But behind this conceptual point of view there are some problems: can execute or not an instruction if they have reached the branch destination or not We need a global program counter with a value broadcasted to all the PEs which

- programming with recursion is impossible since the recursion level is lost through a flat address space;

- a hardware realization requires the addition of a special bus to broadcast the global current address.

at compile time is equivalent to executing the program and is not usually possible. So this global address would have to be replaced by a global time, whose computation

control flow is applied on block structures: parallel gotos are not allowed. Hopefully, if we restrict our interest to structured parallel programming then parallel

#### 3.1 Activity mask

The following properties hold for parallel instruction blocks:

• an instruction block has a beginning and an end;

<sup>&</sup>lt;sup>2</sup>Multiple Instruction stream, Multiple Data stream.

- block, according to a local condition; an instruction block is executed (active) or not (inactive), waiting for an active

- each block is strictly nested into another block or is the main block of the program;

- blocks. Each idle block on a given collection has all the included blocks which by construction, a block inherits the activity of its ancestors, i.e. its surrounding are idle on this collection.

flow exists [MU84]. This method is used in most SIMD [SBM62] and vector computers when parallel control recursion. Instead the activity is stored in a local bit representing the current activity. Thus it is useless to have a global program counter or a global time to tackle

control flow operators), the activity mask is pushed on a stack to recall the history. If the programming model needs parallel control flow imbrications (nests of parallel

## 3.2 Memory write control

controls the writing of the result, thus simulating local execution control. of the previous method is to transform the program in such a way that a local condition Since each computation result can be seen as moving this result in memory, a variation

This method has many drawbacks since:

- results cannot stay in registers for optimization, memory bandwidth is wasted;

- executed instructions may still have side effects like a divide by 0 exception for division.

speculative execution for RISC and VLIW processors. an activity mask. This method is used in computers such as CRAY [Rus78] or GF11 [BDW85], along with Another useful but different application domain of this method is

### 3.3 Local addressing

necessary hardware is simpler. instead of the destination cell. When a PE must be locally turned off, results are written in a dump memory cell Another variation is to use local memory addressing to simulate the memory write-It is still slower than the previous method, but the

## 3.4 Conditional instructions

when these instructions are used to build macrocode only, as in the BLITZEN [BDR87]. in the GF11 microcode. Another simple method is to implement conditional instructions in the PEs like those Unfortunately, compilers have difficulties dealing with them

## 4 Activity counter

an example of a nest of 6 parallel control flow statements, where the first three ones The activity bit stack is only used to determine the level of inactivity. Figure 2 shows

Figure 2: Example of a mask stack.

Table 1: Semantics of the push and pop operations on the activity stack.

| Operation                      | Behavior                      | Precondition                      | Action                 |

|--------------------------------|-------------------------------|-----------------------------------|------------------------|

| $\mathtt{push}(\mathit{cond})$ | $s \leftarrow s + 1$          | $f_0 \neq s + 1$                  | $f_0 \leftarrow f_0$   |

|                                | $a_s \leftarrow cond$         | $(f_0=s+1)\wedge (cond=0)$        | $f_0 \leftarrow s$     |

|                                |                               | $(f_0 = s + 1) \wedge (cond = 1)$ | $f_0 \leftarrow s + 1$ |

| pop                            | $if^a(s>1), s \leftarrow s-1$ | $f_0 \neq s + 1$                  | $f_0 \leftarrow f_0$   |

|                                | $\mathtt{return}(a_s)$        | $f_0 = s + 1$                     | $f_0 \leftarrow s+1$   |

<sup>&</sup>lt;sup>a</sup>Note that if the program is correct, this condition is always true.

third one (represented by "0"). have true conditions (shown as "1" in the figure) and the condition is false after the

the PE remains active. These 1s do not have any intrinsic significance in the stack. is executing the code. Before the first false condition, the stack only contains 1s, indicating that the PE The exit of a conditional block does not change this activity;

activity bits on the stack. Once a 0 bit is pushed on the stack, all the following bits activity is 0 (inactive). on the stack no longer have meaning (represented with a "\*" in Figure 2.) since the When a PE reaches a local false condition, it becomes inactive for all its included The current activity is the logical and of the history of activity, i.e.

#### 4.1 Factorization

should be enough. execution. Therefore, it seems a waste of hardware to use a stack where a plain counter conditional blocks after the first idle block, which indicates when a PE can resume The only useful information in this stack is the number of imbrications of parallel

the current size of the stack, according to Figure 2.  $\mathcal{A} = \bigwedge_{i=0}^{s-1} a_i$ . The PE is active if  $\mathcal{A} = 1$  and idle if  $\mathcal{A} = 0$ . analyze their functionality according to  $f_0$ , the rank of the first 0 on the stack, and s Let push(cond) and pop be the two operations controlling the stack  $(a_i)_{i\in\mathbb{N}}$ . We can The activity of a PE is defined by

an activity true.  $f_0=s+1$  when there is no 0 in any stack element. A pop on an empty stack returns By definition, PEs are all active at initialization time, so  $s=1,\,a_0$ = 1 (active),

only if  $f_0 = s + 1$ , when there is no 0 in the stack. In fact, it is more interesting to do Table 1 gives an operational semantics of the activity stack. A PE is active if and

Table 2: Semantic of the push and pop operations on the activity counter.

|                  | pop                  |                        |                        | $\mathtt{push}(cond)$ | Operation    |

|------------------|----------------------|------------------------|------------------------|-----------------------|--------------|

| c = 0            | $c \neq 0$           | $(c=0) \land (cond=1)$ | $(c=0) \land (cond=0)$ | $c \neq 0$            | Precondition |

| $c \leftarrow 0$ | $c \leftarrow c - 1$ | $c \leftarrow 0$       | $c \leftarrow 1$       | $c \leftarrow c+1$    | Action       |

Table 3: Implementation of the where/elsewhere with an activity counter.

| $c \leftarrow 0$         | (active)      | c = 0           | /elsewhere                 |

|--------------------------|---------------|-----------------|----------------------------|

| $c \leftarrow c - 1$     | (idle)        | $c \neq 0$      | $End\ of\ the\ {	t where}$ |

| $c \leftarrow c$         |               | $c \not \leq 1$ |                            |

| $c \leftarrow \neg c$    | (activatable) | $c \leq 1$      | elsewhere                  |

| $c \leftarrow \neg cond$ | (active)      | c = 0           |                            |

| $c \leftarrow c + 1$     | (idle)        | $c \neq 0$      | $\verb where (cond) $      |

| Action                   | Precondition  | Pr              | Operation                  |

store, as shown on Table 2. The basic manipulations on c are the same as on  $f_0$ : increment or decrement, load or form is easier to implement in hardware and often even in software [Ker89, Ker92]. the variable exchange  $c = s + 1 - f_0$  because only a comparison to 0 is necessary. This

flow can be found in [BL92]. of the equivalence between an activity stack and an activity counter for parallel control The push(cond) when c = 0 can be simplified to  $c \leftarrow \neg cond$ . A more detailed proof

# 4.2 Application to a data parallel language

such as those in the POMPC language. Now we can use this mechanism to implement classical parallel control flow operators

#### **4.2.1** where

languages from FORTRAN 90 to C\*. The basic operator is the where/elsewhere pair which is found in most data parallel

special value that codes for an "activatable" state for the where or elsewhere block. to the last where, i.e. the inactivity level c = 1. The value 1 can be seen here as a The where is equivalent to the push operator but we have to translate the A PE is active in an elsewhere if and only if the PE was inactive due

An implementation is presented in Table 3.

#### 4.2.2 whilesomewhere

iterates a parallel loop until all parallel conditions are false. The continue and break A parallel extension of the C language while is the whilesomewhere construct which

Table 4: Implementation of the whilesomewhere with an activity counter.

| Operation                      | Pı              | Precondition     | Action                                         |

|--------------------------------|-----------------|------------------|------------------------------------------------|

| $\verb whilesomewhere (cond) $ | $c \neq 0$      | (idle)           | $c \leftarrow c + 2$                           |

|                                | c = 0           | (active)         | $c \leftarrow 2 \times \neg cond$              |

| $Loop\ beginning$              | $all\ cond = 0$ | l = 0            | $\leadsto Loop\ exit$                          |

| continue                       | c = 0           | (active)         | $c \leftarrow 1^a$                             |

| break                          | c = 0           | (active)         | $c \leftarrow 2^a$                             |

| $Loop\ end$                    | c = 1           | (re-activatable) | $c \leftarrow 0, \rightsquigarrow Loop\ begin$ |

|                                | $c \neq 1$      |                  | $\leadsto Loop\ beginning$                     |

| Loop exit                      | $c \leq 1$      | (activatable)    | $c \leftarrow 0$                               |

|                                | $c \nleq 1$     | (idle)           | $c \leftarrow c - 2$                           |

<sup>&</sup>lt;sup>a</sup>Relative value to the current whilesomewhere block. See Section 4.2.2.

exit, respectively. are also extended to inactivate a PE until the next iteration or until the whilesomewhere

A PE can be in one of the following states:

- $\dot{}$ inactive before the entry in the whilesomewhere block, thus it will remain inactive in this block;

- 2. active at the whilesomewhere entry;

- ယ္ inactive at the whilesomewhere entry because the local condition is false; the PE will remain inactive until the whilesomewhere exits;

- inactive in the whilesomewhere until the whilesomewhere exits because break of ھ

- Ċ inactive in the whilesomewhere until the next iteration after executing continue; ھ

until the whilesomewhere exits. They can be implemented in the same way. States 3 and 4 are not different once the break is executed; the PE remains idle

incrementation in the first row of the implementation presented on table 4. nisms. It is implemented by reserving a protected value 1 in the counter by a double In comparison with the where/elsewhere, only point 5 requires additional mecha-

is used for the states 3 and 4 (line 2 and row 4 of Table 4. The value c=1 is used to implement state 5 (the continue) and the value c=

repeated on each PE.  $begin/Loop\ end\ exiting\ on\ all\ cond=0\ condition.$  On an MIMD machine, the loop is In a real implementation on an SIMD machine, there is a scalar loop around *Loop*

marked with "a" must be relative to the current whilesomewhere block, i.e. augmented where/elsewhere exit instead of a break or a continue. It is the reason why the value in a where/elsewhere. A more complex but common case is when the continue or the break are enclosed In this case,  $c \leftarrow 1$  or  $c \leftarrow$ 2 could be thought of as an

Table 5: Implementation of the switchwhere with an activity counter.

| Operation                      | Pı                   | Precondition                                             | Action               |

|--------------------------------|----------------------|----------------------------------------------------------|----------------------|

| $\mathtt{switchwhere}(value)$  | $c \neq 0$           | (idle)                                                   | $c \leftarrow c + 2$ |

|                                | c = 0                | (active)                                                 | $c \leftarrow 1$     |

| ${\tt case}\ {\it constant}$ : | $(c=1) \wedge (c=1)$ | $(c=1) \land (value = 	extbf{constant})  c \leftarrow 0$ | $c \leftarrow 0$     |

| break                          | c = 0                | (active)                                                 | $c \leftarrow 2^a$   |

| default :                      | c = 1                | (activatable)                                            | $c \leftarrow 0$     |

| switchwhere $closing$          | $c \leq 1$           |                                                          | $c \leftarrow 0$     |

|                                | $c \not\leq 1$       |                                                          | $c \leftarrow c - 2$ |

where/elsewhere. aMust be relative to the current switchwhere block, if the break is included in one or more

and the continue or the break. by the number of where/elsewhere imbrications between the whilesomewhere block

translation of for to while in C. a data parallel for, a forwhere, is derived from the whilesomewhere according to the tion of a while into a do/while in the C language. Similarly, the implementation of The dowhere/whilesomewhere version is derived from Table 4 as the transforma-

#### 4.2.3 switchwhere

also has several states. A PE can be: The compilation of a switchwhere, the parallel extension of the language C switch,

- 1. inactive before the switchwhere:

- 2. active in a case (after matching a value) or in a default;

- inactive in a case, waiting for a matching value;

- inactive in the switchwhere because of a break, until the switchwhere exit.

use is c = 1 for the state 3 and c = 2 for the state 4, as shown in Table 5. The break is similar to the whilesomewhere one. An example of state coding we

#### 4.2.4 Parallel return

used in parallel control flow in the example of Figure 3. The parallel return allows a parallel function to return a parallel value and can be

or a switchwhere and has the following states: the exit of the current function. It is very similar to the break in a whilesomewhere In this case, we want the PEs that execute the parallel return to become idle until

- 1. a PE is active at the function entry;

- 2. a PE is inactive at the function entry;

- ယ္ ಶ PE is inactive until the end of the function because it has executed a return.

```

collection a_coll double fabs(a_coll double x)

where (x > 0)

return -x;

return x;

```

Figure 3: Example of a generic parallel absolute value function in POMPC.

Table 6: Implementation of the parallel return with an activity counter.

| Operation         | Preco      | Precondition | Action                 |

|-------------------|------------|--------------|------------------------|

| $Function\ entry$ | $c \neq 0$ | (idle)       | $c \leftarrow c+1$     |

| return            | c = 0      | (active)     | $c \leftarrow c + 1^a$ |

| Function closing  | $c \neq 0$ | (idle)       | $c \leftarrow c - 1$   |

|                   |            |              |                        |

blocks. <sup>a</sup>Must be relative to the current function block, if the return is included in some parallel conditional

C = 1 is reserved in the counter, as shown in Table 6. In order to constrain the visibility of the parallel return of the function, a value

# 5 Activity counters versus activity stacks

computers. of the activity counter method and activity stack method, both for SIMD and MIMD In order to develop choice arguments, we have to analyze the time and space complexity

## 5.1 On an SIMD machine

cycles of duration t to do an activity counter operation. conditional blocks are imbricated. If each PE has an L-bit operator, a PE needs  $\lceil \log_L c \rceil$ The counter method needs a counter with  $\log_2 c$  bits per PE if at most c levels of parallel

are synchronous and the stack pointer can be: needs a stack pointer to manage the stack. Since the execution is SIMD, all the stacks The activity stack needs only 1-bit manipulation on each PE and takes a time t, but

- centralized on the scalar processor which broadcasts its value to the PES;

- $\bullet$  distributed with local pointers which evolve synchronously.

the local stack pointers in the second case, for a N-PE computer. plus  $\lceil \log_L c \rceil$  bits for the global stack pointer in the first case and  $N\lceil \log_L c \rceil$  bits for on each PE. The hardware complexity is c for a stack of 1 bit elements in each case, on the PEs. In the second case, a time  $t\lceil \log_L c \rceil$  is needed to control the stack pointer In the first case, it takes a time T on the scalar processor and the time is negligible

Table 7: Complexity of the activity counter and activity stack methods.

| Parallel               | Comp       | Computing complexity                                           | Hardware                        | #         |

|------------------------|------------|----------------------------------------------------------------|---------------------------------|-----------|

| conditioning           | scalar     | parallel                                                       | complexity                      | broadcast |

| Stack (global pointer) | T          | t                                                              | $Nc + \lceil \log_2 c \rceil$   | Ľ         |

| Stack (local pointers) | $\epsilon$ | $t(1+\lceil \log_L c \rceil) \mid N(c+\lceil \log_2 c \rceil)$ | $N(c + \lceil \log_2 c \rceil)$ | 0         |

| Activity counters      | $\epsilon$ | $t\lceil \log_L c \rceil$                                      | $N\lceil \log_2 c \rceil$       | 0         |

|                        |            |                                                                |                                 |           |

The complexity of the three previous methods are summarized up in Table 7.

slices. 1-bit. This method is used on computers such as the CM-2 [Thi87] or the MP-1 [Bla90]. the  $t\lceil \log_L c \rceil$  required to deal with a local stack pointer or activity counter by L-bit pointer computation only uses few cycles, and even the broadcast is often shorter than pointer. Indeed, the scalar processor is often larger and more powerful, so the stack interesting to subcontract the computation to the scalar processor with a global stack If the computer has only fine grain PES, typically L = 1 or 4 bits, it is more Moreover, 1-bit PEs have the advantage that they easily access memory with

bus which is time-multiplexed between all the PEs of a chip. compared with the data bus throughput, since there often is a common address data a fast memory indirection, and more generally a sufficient data address bus throughput nately, a fine grain PE rarely has a large enough adder on the address bus to keep with in memory must be fast enough to compensate for the lack of fast broadcast. Unfortubroadcast is too expensive and a local indirection is available. But the local indirection The activity stack with a local stack pointer is well suited for small PES, when a

size allows a counter hardware implementation on the PE that minimizes latency. counter clearly avoids wasting memory bandwidth. The drastic reduction in storage to deal with 1-bit accesses in memory required by the activity stack, so the activity is slow in comparison to the PE cycle time. A large data bus to memory is not adapted machines. These computers often have short cycle time and the local memory access The activity counter algorithm is particularly interesting for coarse grain SIMD

GF11 [BDW85], OPSILA [AB86] and more recently the CM-5 [Thi91] or the MP-2 The activity counter could have been applied efficiently in the ILLIAC IV [BBK+68],

software and can improve compilers for existing architectures. in hardware instead of emulating it in software. However, the method is also useful in If we were designing a new SIMD computer, we would implement the activity counter

## 5.2 On an MIMD machine

stack pointer and thus only local pointers or activity counters are necessary. that since there is no scalar processor, it is not interesting to have a global activity The complexity of our method for an MIMD machine is the same as in table 7 except

on each PE reduces to  $\mathcal{O}(\log c)$  the hardware complexity to store the activity. the coarse grain PEs which are in most MIMD computers. Besides, the activity counter PES. Activity counters can avoid the 1-bit stack management, specially inefficient on As for the SIMD computers, the same conclusions arise according to the size of the

hardware since local conditional jumps are used in fine to efficiently emulate the activity But unlike SIMD computers, it is not worth implementing the activity counter in

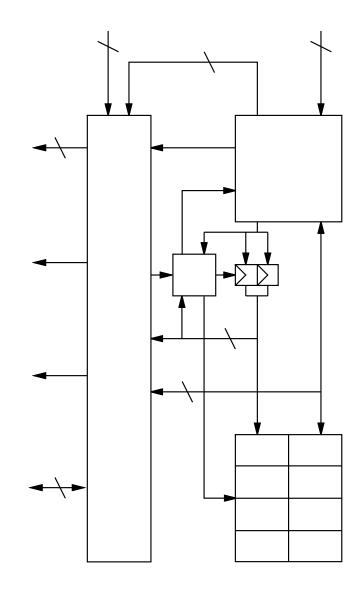

Figure 4: PE node synoptic in the POMP computer.

corresponding to the counter value. Thus, it would need incessant exchanges between a PE, its counter and its memory.

### 6 Implementation

and a compiler for the POMPC language which uses activity counters if they exist or In the POMP project, we have studied a hardware implementation for the POMP machine emulates them if not.

## 6.1 Hardware application

they are coarse grain processors (Motorola MC88100) the activity counter is valuable. In the POMP SIMD computer [HKMP91, Ker92], off-the-shelf RISC PES are used. Since

broadcast, exception control,...). has other functions that allow the machine to run in an SIMD mode (communications, in a companion circuit made with a FPGA (named HyperCom in figure 4) which also It was not possible to implement such a counter inside the processor, so it was done

through a fast PAL that does not slow down the pipelined processor bus. the FPGA which controls the ready signal (CRO:CR1) of the instruction bus of the PE and switchwhere. The control of the instruction execution in the PE is performed by parallel conditional blocks and a comparator to  $0,\!1$  and 2 to speed up whilesomewhere The activity counter is implemented with a 32-bit counter, allowing up to  $2^{32}$  nested

added to the 32-bit basis instruction of the PE. These instructions are produced by The parallel conditional execution is supervised by the 8-bit HyperCom instruction

indicating to the HyperCom it has to spy the bus. optimally by initializing a read on the PE at the memory address plus a major offset the data bus. DMA operation between the counter and the memory is done simply but activity counter for complex parallel control flow and for virtualization goals through the scalar processor, another MC88100 with a VLIW coupling. Each PE can access its

#### 6.2 Compilation

has been written and generates C\*, MPL and C programs respectively. A compiler of PompC for the cm-2, the mp-1 and Unix workstations for simulation

1-bit operators and virtualization is present in  $C^*$ . The compiler for the CM-2 is not using activity counters since the PEs only have

activity counters are used to deal with parallel control flow in the compiler of POMPC parallel variables with the same size as the physical machine can be used. Thus soft On the contrary, the MP-1 has larger 4-bit PEs and MPL does not virtualize, i.e. only

for the next collection are loaded instead. another collection, the current activity counters are saved in memory and new values an activity counter. [PCMP85], but they use extents of parallelism to manage an activity stack instead of scalar operations, are sliced in the same manner as in the ACTUS compiler described in The imbrication of parallel control flow operators, merging different collections and In the POMPC compiler, each time there is an operation affecting

an activity counter in hardware. Since the POMP prototype is not yet finished, we do not have a compiler which uses

#### 7 Related work

But other methods based on a different principle can be found in the literature. In Section 4 we presented an optimization of the activity concept described in Section 3.

and sometimes to modify the algorithm. place. Unfortunately, this method needs the programmer to restructure the program At the end of the computations, the dense vectors are scattered back to their original each variable is a dense vector and the vector processor can be used efficiently on it. different parallel variables corresponding to the subdomains of the problem. performance on sparse problems. Computations on subdomains are put together in A common solution for vector computers is the use of  $\mathit{scatter/gather}$  to boost vector

heads (a lot of where and many collections concerning few operations). elsewhere well-balanced) or it may be very important due to communication overbig computation kernel concerning only one collection in a where, a where and an be negligible compared with an activity method, depending of programs and data (a compile time, it is not trivial. ity method and scatter/gather. method does not implement complexity evaluation to choose between classical activter/gather couple, i.e. a global communication before and after the computation. The LISP compiler to SIMD computers. Each subdomain selection is transformed in a scat-A generalization of this method is presented in [Ble89, BS90] for the Parallation But it is necessary because the scatter/gather may Even when this complexity evaluation is possible at

activity method is advisable. Since we improve the activity method, we also extend its In the first case the scatter/gather method is better but in the second case an

#### 8 Conclusion

MIMD computers, and compilers for languages with collection oriented data parallelism. We have developed a new method to deal with nested parallel control flow for SIMD and

a henceforth superfluous load. bit stack management, a global address broadcast and relieves the scalar processor of coarse grain parallel computers since it avoids an inefficient indirection in memory, 1bits of memory used to keep track of the PE history. The method is more suited to This technique allows a reduction to a straight logarithmic term of the size in

imbricated case it seems a better choice. tivity counter method can often be replaced by MIMD local control flow, for complex or not possible, or if complex sub-array selections cannot be determined. example, if different collections are mixed, interprocedural analysis is not performed ers when the imbricated parallel control flow cannot be resolved at compile time. For The optimization is also interesting for compilers targeted to modern MIMD comput-

## 9 Acknowledgements

all the members of the POMP team since the beginning of the project: Philippe Théodore Papadopoulo and Pierre Chicourrat. Matherat, Philippe Hoogvorst, César Douady, Patrice Ossona Demendez, The authors of this paper would like to acknowledge many useful discussions with

the domain and our work. for their discussions on SIMD semantics in parallel control flow and for their interest for Special thanks are due to Luc Bougé and his team, especially Jean-Luc Levaire.

propriate suggestions. François IRIGOIN and Pierre JOUVELOT for their invaluable comments and their ap-At last but not the least, the authors are indebted to Kathryn Mackinley,

#### References

- [AB86] M. AUGUIN and F. BOERI. "The OPSILA Computer". In INRIA, editor, Parallel Algorithms & Architectures, pages 143–153. North-Holland, 1986.

- [BBK<sup>+</sup>68] George H. Barnes, Richard M. Brown, Maso Kato, David J. Kuck, Daniel L. actions on Computers, C-17(8):746-757, August 1968. SLOTNICK, and Richard A. STOKES. "The ILLIAC IV Computer". IEEE Trans-

- [BDR87] Donald W. Blevins, Edward W. Davis, and John H. Reif. "Processing Element Technical Report TR87-22 Revision 1, Microelectronics Center of NC, 1987 and Custom Chip Architecture for the BLITZEN Massively Parallel Processor"

- [BDW85]John Beetem, Monty Denneau, and Don Weingarten. "The GF11 Supercomputer". In  $SIGARCH\ 85$ , pages 108–115. The Institute of Electrical and Electronics Engineers, Inc., 1985.

- [BL92] Luc Bougé and Jean-Luc LEVAIRE. "Control structures for data-parallel SIMD 8(3-4):363-378, 1992 languages: semantics and implementation". Future Generation Computer Systems.

- [Bla90]Tom Blank. "The MasPar MP-1 Architecture". In IEEE, editor, IEEE Compton *Spring 1990*, February 1990.

- [Ble89]Guy E. Blelloch. "Scan Primitives and Parallel Vector Models". PhD thesis ber 1989. MIT/LCS/TR-463. Laboratory for Computer Science — Massachusetts Institute of Technology, Octo-

- [BS90]Guy E. Blelloch and Gary W. Sabot. guages onto Massively Parallel Computers". Journal of Parallel and Distributed Computing, 8(2):119–134, February 1990. "Compiling Collection-Oriented Lan-

- [Fly66]Michael J. Flynn. *IEEE*, 54(12):1901–1909, December 1966. "Very High-Speed Computing Systems". Proceedings of the

- [HKMP91] Philippe Hoogvorst, pub/reports/liens/liens-91-5.A4.ps.Z. Verlag, June 1991. Developments". In PARLE '91 Parattet Architectures und pumpy--y-volume 505(I), pages 83–100. Lecture Notes in Computer Science, "POMP or How to Design a Massively Parallel Machine with In PARLE '91 Parallel Architectures and Languages Europe. Available by ftp anonymous on spi.ens.fr in the Ronan Keryell, Philippe Matherat, and Nicolas

- $[HLJ^{+}91]$ Philip J. Hatcher, Anthony J. Lapadula, Robert R. Jones, Michael J. Quinn, Parallel Programming, volume 26(7), pages 73–82, July 1991. SIGPLAN Notices. and Ray J. Anderson. "A Production-Quality C\* Compiler for Hypercube Multicomputers". In Third ACM SIGPLAN Symposium on Principles & Practice of

- [Ker 89]Ronan KERYELL. "POMP2: D'un Petit Ordinateur Massivement Parallèle". Rapport de magistère, LIENS — Ecole Normale Supérieure, October 1989.

- [Ker92]Ronan Keryell. Laboratoire d'Informatique de l'Ecole Normale Supérieure — Université Paris XI à Base de Processeurs RISC — Concepts, Etude et Réalisation". PhD Thesis, "POMP: d'un Petit Ordinateur Massivement Parallèle SIMD

- [Mas91]MasPar Computer Corporation. "MasPar Parallel Application Language (MPL) 1991. Software Version 2.0. Reference Manual, document part number: 9302-000, revision: a4 edition, March

- [MU84]Kenichi MIURA and Keiichiro UCHIDA. Speed Computing, volume F7, pages 59–73. IEEE Computer Society Press, 1984. 100/VP-200 ". In Proceedings of NATO Advanced Research Workshop on High "Facom Vector Processor System: VP-

- [Par92]Nicolas Paris. pub/reports/liens/liens-92-5-bis.A4.ps.Z. port LIENS-92-5-bis, Laboratoire d'Informatique de l'École Normale Supérieure, March 1992. Available by ftp anonymous on spi.ens.fr in the file "Definition of POMPC (Version 1.99)" Technical Re-

- [PCMP85]Ronald H. Perrott, Danny Crookes, Peter Milligan, and W. R. Martin Purdy. "A Compiler for an Array and Vector Processing Language". *IEEE Trans*actions on Software Engineering, SE-11(5):471-478, May 1985.

- [Per79]R. H. PERROTT. "A Language for Array and Vector Processors". tions on Programming Languages and Systems, 1(2):177-195, October 1979 ACM Transac-

- [Rus78] Richard M. RUSSEL. ACM, 21(1):63-72, January 1978. "The CRAY-1 Computer System". Communications of the

- [SBM62] Daniel L. SLOTNICK, W. Carl BORCK, and Robert C. MCREYNOLDS. "The SOLOMON Computer". In Proceedings of the Fall 1962 Eastern Joint Computer Conference, pages 97–107, December 1962. "The

- [Thi87] Thinking Machine Corporation. "Connection Machine Model CM-2 Technical Summary", April 1987. HA87-4.

- [Thi90] Thinking Machine Corporation. "C\* Programming Guide", November 1990. Version 6.0.

- [Thi91] Thinking Machine Corporation. "The Connection Machine CM-5 Technical Summary", October 1991.

- [Wav91] Wavetracer Inc. Wavetracer Inc. "The multiC Programming Language — User Documentation", pub-00001-001-1.01 edition, September 1991.